# 112-GHz, 157-GHz, and 180-GHz InP HEMT Traveling-Wave Amplifiers

Bipul Agarwal, Adele E. Schmitz, J. J. Brown, Mehran Matloubian,

Michael G. Case, *Senior Member, IEEE*, M. Le, M. Lui,

and Mark J. W. Rodwell

**Abstract**—We report traveling-wave amplifiers having 1–112 GHz bandwidth with 7 dB gain, and 1–157 GHz bandwidth with 5 dB gain. A third amplifier exhibited 5 dB gain and a 180-GHz high-frequency cutoff. The amplifiers were fabricated in a 0.1- $\mu$ m gate length InGaAs/InAlAs HEMT MIMIC technology. The use of gate-line capacitive-division, cascode gain cells and low-loss elevated coplanar waveguide lines have yielded record bandwidth broad-band amplifiers.

**Index Terms**—Distributed amplifier, MMIC, traveling-wave amplifier, TWA.

## I. INTRODUCTION

**B**ROAD-BAND amplifiers find applications as gain blocks in multigigabit fiber-optic receivers and as preamplifiers in broad-band instrumentation. Future 100- and 160-Gbit/s optical transmission systems will require amplifiers with very high bandwidths. High-electron mobility transfer (HEMT) traveling-wave amplifiers (TWA's) with  $\simeq$ 100 GHz bandwidths have been demonstrated [1]–[3]. Pusl *et al.* [2] used capacitive voltage division [4] on the gate synthetic line to obtain 11 dB gain over a 1–96-GHz bandwidth. Capacitive division decreases the frequency-dependent losses on the gate synthetic transmission line. With these losses reduced, the number of TWA cells can be increased to increase TWA gain. In this manner, the feasible gain for a given design bandwidth is increased. With very small capacitive division ratios, losses associated with the HEMT input resistance are reduced to the point where other loss mechanisms are significant. If the dominant loss mechanisms are the HEMT series input resistance and shunt output conductance, the capacitive-division TWA can obtain gain–bandwidth products limited by the transistor power gain cutoff frequency  $f_{\max}$ . If a cascode cell is used as the transconductance element with the TWA, the gain–bandwidth product can be increased well beyond the transistor  $f_{\max}$ .

For design bandwidths above 100 GHz, TWA design is strongly impacted by both the losses and physical dimensions of the synthetic transmission lines. With small capacitive division ratios and design bandwidths above 100 GHz,

Manuscript received March 20, 1998; revised August 15, 1998. This work was supported by DARPA under the Thunder and Lightning program and a California/Hughes MICRO no. 8960808.

B. Agarwal and M. J. W. Rodwell are with the Department of Electrical and Computer Engineering, University of California, Santa Barbara, CA 93106 USA (e-mail: rodwell@ece.ucsb.edu).

A. E. Schmitz, J. J. Brown, M. Matloubian, M. G. Case, M. Le, and M. Lui are with Hughes Research Laboratories, Malibu, CA 90265 USA.

Publisher Item Identifier S 0018-9480(98)09230-8.

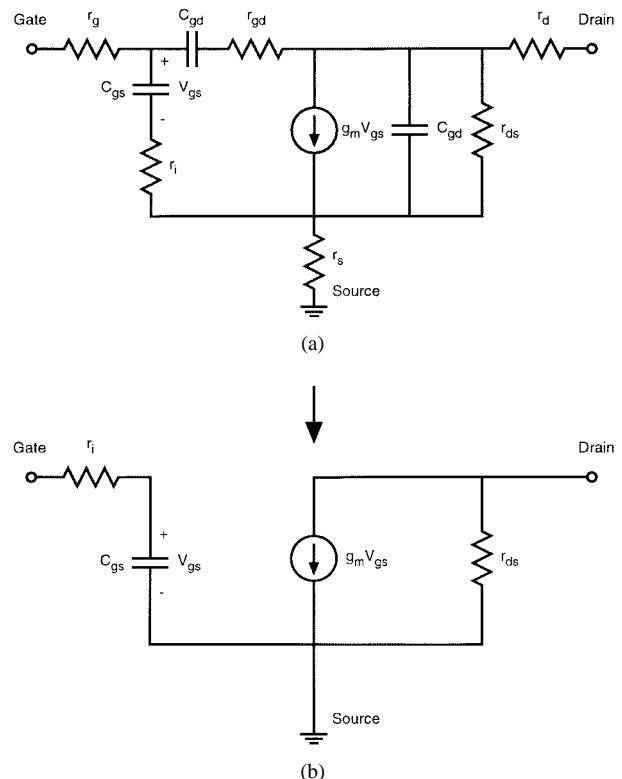

Fig. 1. Small-signal equivalent circuit of (a) a HEMT and (b) a simplified model.

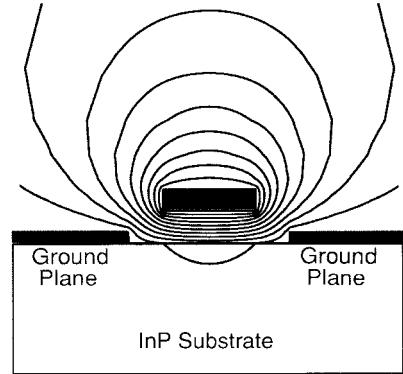

transmission-line skin-effect losses impact the feasible amplifier bandwidth, and the required transmission-line lengths become shorter than the physical dimensions of the HEMT's, making the physical layout unrealizable. By using coplanar waveguide (CPW) transmission-lines with the center conductor raised  $\sim$ 2  $\mu$ m above the substrate [5], [6], the CPW effective dielectric constant is reduced, reducing the line skin-effect losses and increasing the wave velocity. Bandwidth is improved, and the physical layout becomes realizable.

Using gate line capacitive division and elevated CPW, we have fabricated TWA's with 1–112 GHz bandwidth at 7–10 dB gain and 1–157 GHz bandwidth at 5 dB gain. A third amplifier, processed on a wafer with a higher HEMT  $f_{\tau}$ , exhibited 5 dB gain and a 180-GHz high-frequency cutoff.

## II. THEORY

Traveling-wave amplifiers are broad-band circuits whose gain–bandwidth product substantially exceeds the transistor

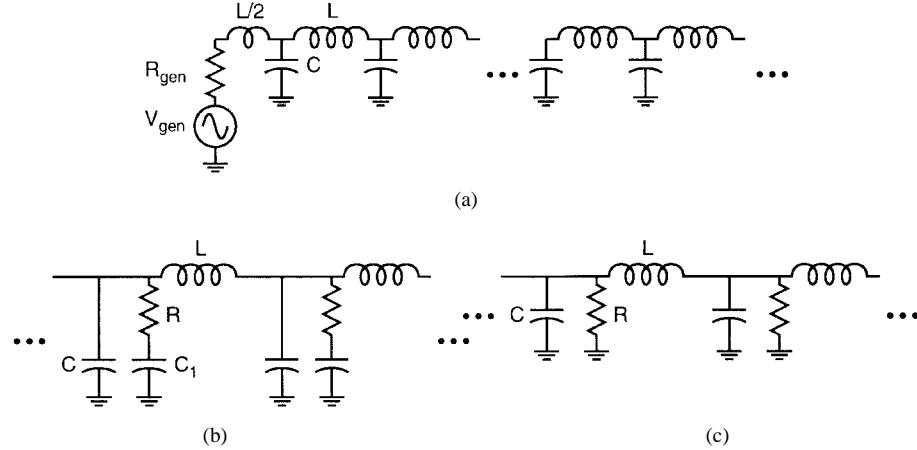

Fig. 2. Periodic synthetic transmission lines (a) without loss, (b) with frequency-dependent loss, and (c) with frequency-independent loss.

current-gain cutoff frequency  $f_\tau$ . In TWA's, transistor input and output capacitances are absorbed into synthetic transmission lines (LC ladder networks). Amplifier bandwidth is then limited by the synthetic-line (Bragg) cutoff frequency, by frequency-dependent losses associated with the transistor input and output resistances, and by transmission-line losses. TWA design theory is described clearly in [7]. In the analysis below we show [2], [8] that with gate-line capacitive division, the gain-bandwidth product of a common-source TWA approaches the transistor  $f_{\max}$ . With cascode gain cells and capacitive division, feasible gain at a given design bandwidth is, in principle, constrained by the cascode cells' maximum available gain, although circuit size, power consumption, and line loss considerations will set feasible gains well below this limit.

Fig. 1 shows complete and simplified HEMT small-signal equivalent circuit models. Because of feedback through  $C_{gs}$ , TWA analysis with the full HEMT model is complex, and the simplified model of Fig. 1(b) will instead be used. Fig. 1(b) models only the dominant parasitics, e.g., the gate-source capacitance  $C_{gs}$ , the input resistance  $r_i$ , the transconductance  $g_m$ , and the output resistance  $r_{ds}$ . These elements scale with HEMT gate width (device area)  $W_g$ , with  $g_m$  and  $C_{gs}$  proportional to  $W_g$  and  $r_i$ , and  $r_{ds}$  proportional to  $W_g^{-1}$ .  $f_\tau = g_m/2\pi C_{gs}$  and  $f_{\max} = f_\tau \sqrt{r_{ds}/4r_i}$  are independent of  $W_g$ .

Design relationships for synthetic lines are now required. The synthetic line of Fig. 2(a) is lossless for frequencies below the Bragg cutoff frequency  $f_B = 1/\pi\sqrt{LC}$ , but has very high attenuation for  $f > f_B$ . For frequencies well below the Bragg frequency, the synthetic line has characteristic impedance  $Z_0 = \sqrt{L/C}$  and per-section delay  $T = \sqrt{LC}$ . If a small series resistance  $R$  is added with a portion  $C_1$  of the shunt capacitance as in Fig. 2(b), the line becomes lossy. The frequency-dependent loss per section is given by  $e^{-\alpha}$ , where

$$\alpha \simeq 4\pi^2 f^2 C_1^2 R Z/2. \quad (1)$$

Adding a large shunt loading resistance  $R$  as in Fig. 2(c) introduces a frequency-independent loss per section  $e^{-\alpha}$ ,

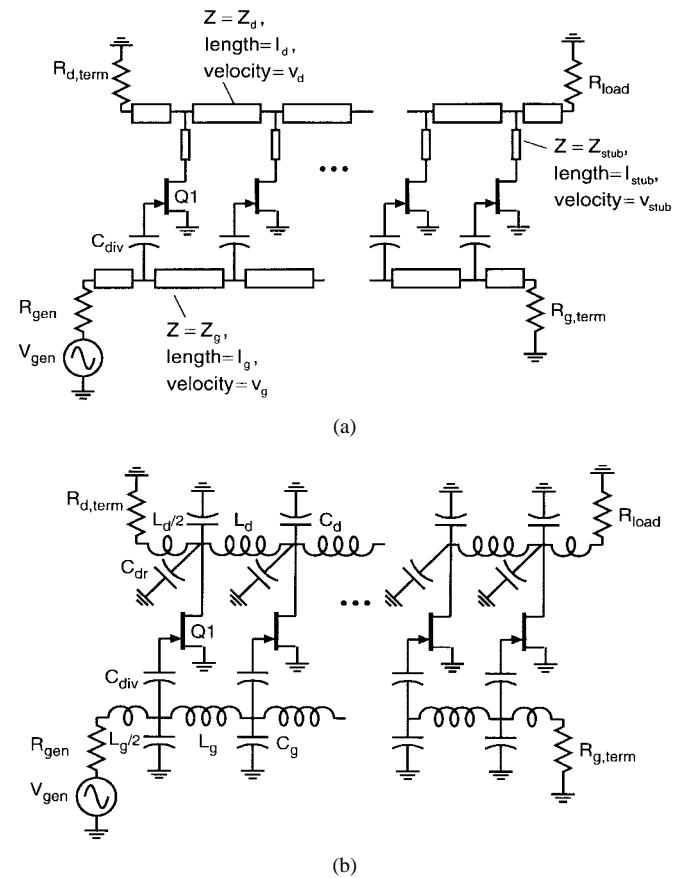

Fig. 3. Circuit diagram of the capacitive-division traveling-wave amplifier with (a) transmission-line tuning sections and (b) approximate equivalent LC model.

where

$$\alpha \simeq Z/2R. \quad (2)$$

Fig. 3(a) shows a HEMT capacitive-division traveling-wave amplifier. In this circuit, inductive and capacitive reactances are implemented through transmission line sections. In both the gate and drain circuits, inductors are approximated with high-impedance line sections ( $Z_g$  and  $Z_d$ ), while shunt capacitors are implemented with series stubs ( $Z_{\text{stub}}$ ). These line sections

Fig. 4. Small-signal model of the amplifier.

are short in comparison with a wavelength and can be modeled with  $LC$   $\pi$ -sections, resulting in the circuit model of Fig. 3(b). The gate-circuit series lines of characteristic impedance  $Z_g$ , phase velocity  $v_g$ , and length  $l_g$  are modeled in Fig. 3(b) as the inductances  $L_g = Z_g l_g / v_g$  and the capacitances  $C_g = l_g / v_g Z_g$ . Similarly, the drain-circuit series lines of characteristic impedance  $Z_d$ , phase velocity  $v_d$ , and length  $l_d$  are modeled as  $L_d = Z_d l_d / v_d$  and  $C_d = l_d / v_d Z_d$ , while the drain series stubs are modeled as capacitances  $C_{dr} = l_{\text{stub}} / v_{\text{stub}} Z_{\text{stub}}$ .

Using the simplified *LC* representation, Fig. 4 shows the TWA small-signal equivalent circuit. Both the gate and drain synthetic lines will be designed for characteristic impedance  $Z_0$ , e.g.,  $Z_{0,g} = Z_{0,d} = Z_0$ . The gate (input) and drain (output) transmission lines are terminated with the synthetic-line characteristic impedance  $R_{g,term} = R_{d,term} = Z_0$ , and the generator and load impedances are both equal to  $Z_0$ .  $C_{div}$  is the gate-line division capacitor and  $M$  is the capacitive-division ratio

$$M = C_{\text{div}} / (C_{\text{div}} + C_{\text{qs}}). \quad (3)$$

The case  $M = 1$  corresponds to a TWA without capacitive division.  $C_{dr}$ , the stub capacitance, is introduced to adjust the drain-line per-section delay  $T_d$ . In design,  $T_d$  is made equal to the gate-line per-section delay  $T_g$ , e.g.,  $T_g = T_d = T$ . This results in the drain currents of the  $N$  HEMT's collectively adding in-phase at the amplifier output.

For the gate line, the loaded characteristic impedance, per-section delay, Bragg cutoff frequency, and per-section attenuation are

$$\begin{aligned} Z_{0,g} &= Z_0 = \sqrt{L_g/(C_g + MC_{gs})} \\ T_g &= T = \sqrt{L_g(C_g + MC_{gs})} \\ f_{B,g} &= 1/\pi \sqrt{L_g(C_g + MC_{gs})} \\ \alpha_b &\simeq 4\pi^2 f^2 M^2 C_{gs}^2 r_i Z_o / 2. \end{aligned} \quad (4)$$

Similarly for the drain line, the loaded characteristic impedance, per-section delay, Bragg cutoff frequency, and

per-section attenuation are

$$\begin{aligned} Z_{0,d} &= Z_0 = \sqrt{L_d/(C_d + C_{dr})} \\ T_d &= T = \sqrt{L_d(C_d + C_{dr})} \\ f_{B,d} &= 1/\pi\sqrt{L(C_d + C_{dr})} \\ \alpha_d &\simeq Z_o/2r_{ds}. \end{aligned} \quad (5)$$

Equalizing  $Z_{0,g} = Z_{0,d}$  and  $T_g = T_d$  simply requires that  $L_g = L_d$ ,  $C_g = C_d$ , and  $C_{dr} = MC_{gs}$ .

Gain-bandwidth limits can now be derived. For each transistor, the input signal propagates through a section of the gate line before driving that transistor's input and producing a drain current  $Mg_mV_{gs}$ . The drain current generates a forward wave on the drain line of amplitude  $Mg_mV_{gs}Z_o/2$ . Given that we have set  $T_g = T_d$ , all HEMT outputs add in phase. The overall amplifier gain is

$$A_v = -NMg_mZ_o/2. \quad (6)$$

The number of HEMT sections is limited by line losses. The input voltage to the  $N$ th stage is attenuated by  $e^{-(N-1/2)\alpha_g}$ . Setting the total gate line losses to  $e^{-1/2} \simeq -4$  dB, the maximum number of transistors  $N_{\max}$  for a given desired bandwidth  $f_{BW}$  is given by

$$4\pi^2 f_{BW}^2 N_{\max} M^2 C_{gs}^2 r_i Z_o \simeq 1. \quad (7)$$

Beyond  $N_{\max}$ , the transistors do not contribute to the output voltage as the driving gate voltage is small. From the drain line losses, the voltage due to the first stage is attenuated by  $e^{-(N-1/2)\alpha_d}$  at the output. Setting the total drain line losses to  $e^{-1/2} \simeq -4$  dB, the maximum number of transistors  $N_{\max}$  is thus given by

$$N_{\max} Z_o / 2r_{ds} \simeq 1. \quad (8)$$

If there are more stages than  $N_{\max}$ , the output of the first transistor is severely attenuated and does not contribute significantly to the output voltage. Using (6)–(8), the gain–bandwidth product is given by

$$A_v f_{BW} = g_m / 2\pi C_{gs} \sqrt{r_{ds}/4r_i} = f_{\max}. \quad (9)$$

The maximum TWA gain-bandwidth product is equal to the transistor  $f_{\max}$ . In this analysis, transmission line skin-effect and radiation losses have been neglected. It is important to note that (7) and (8) can only be simultaneously satisfied if capacitive-division is used. Consequently, without capacitive division, the TWA gain-bandwidth product falls below  $f_{\max}$ .

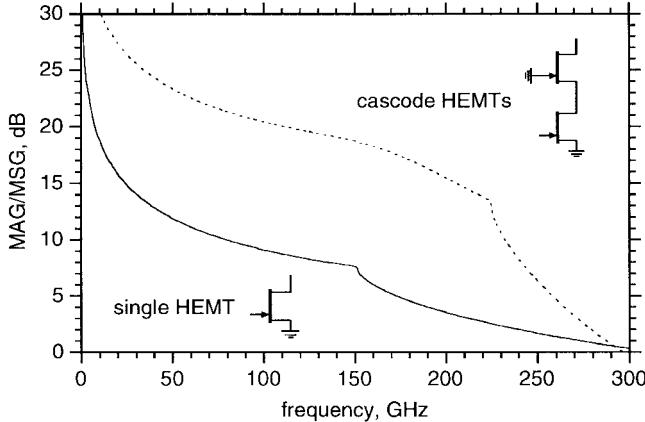

Higher TWA gains at a given design bandwidth are obtained using cascode cells. As a consequence of its high output impedance, the power gain of a cascode pair is considerably higher than for a common-source stage. Fig. 5 compares the maximum available gain (MAG) and maximum stable gain (MSG) of cascode and common-source gains for the specific HEMT's used in this work. The output impedance of the cascode pair is very high ( $r_{ds}[1 + g_{mr}r_{ds}]$  at moderate frequencies), and in a first analysis drain-line losses can then

Fig. 5. Maximum available gain of a single transistor and cascode-connected transistors.

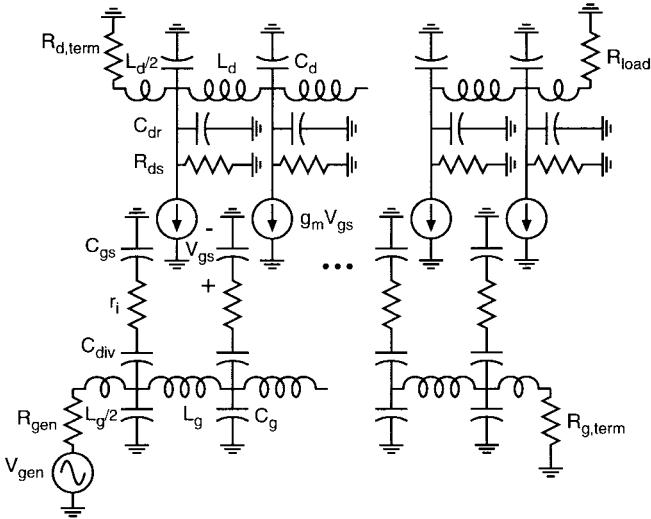

Fig. 6. Schematic circuit diagram of the cascode capacitive-division traveling-wave amplifier.

be neglected. With this assumption, the following design equations can be derived:

$$\begin{aligned} \alpha_g &\simeq 4\pi^2 f^2 M^2 C_{gs}^2 r_i Z_o / 2 \\ \alpha_d &\simeq 0 \\ A_v &= -NMg_m Z_o / 2 \\ 4\pi^2 f_{BW}^2 N_{\max} M^2 C_{gs}^2 r_i Z_o &\simeq 1. \end{aligned} \quad (10)$$

Examining the gain-bandwidth product for this amplifier we obtain

$$A_v f_{BW}^2 = f_\tau / 4\pi M C_{gs} r_i. \quad (11)$$

From (11) it appears that the gain-bandwidth product can be increased arbitrarily to very high values by using aggressive capacitive-division (smaller  $M$ ). This conclusion results from neglecting the cascode output conductance and is misleading. The amplifier gain is ultimately limited by the maximum available power gain of the cascode cell at any given frequency. This is not evident from the above analysis because the output impedance of a cascode cell is  $\simeq r_{ds}(1 + g_m r_{ds})$  only at low frequencies, and an accurate drain line loss analysis is quite complex. The frequency dependent output impedance of the cascode can be derived by nodal analysis using the model of

Fig. 7. Cross section and constant-potential profiles of elevated coplanar waveguide. With the center conductor raised 2  $\mu\text{m}$  above the substrate, losses are reduced and wave velocity increased.

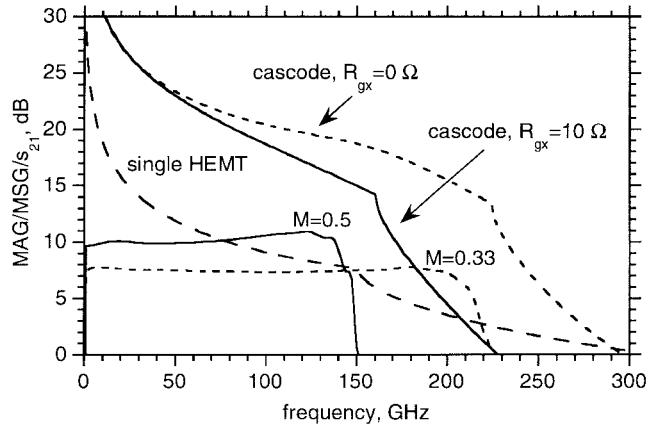

Fig. 8. Simulated gain-frequency characteristics of the two traveling-wave amplifiers.

Fig. 1(b) and is given approximately by

$$Z_{\text{out}} = \begin{cases} r_{ds}(1 + g_m r_{ds}), & \text{for } \omega \ll 1/C_{gs} r_{ds} \\ r_{ds} + g_m r_{ds}/j\omega C_{gs}, & \text{for } \omega \gg 1/C_{gs} r_{ds}. \end{cases} \quad (12)$$

This  $Z_{\text{out}}$  contributes to drain-line losses, with  $\alpha_d \simeq (f/f_\tau)^2 (Z_o/2r_{ds})$ , as per earlier analysis. In the idealized case where drain-line transistor  $Z_{\text{out}}$  losses dominate, a detailed analysis shows that the TWA gain can approach the maximum available gain of the cascode cell. However, generally  $Z_{\text{out}}$  for the cascode is sufficiently high that drain-line losses due to the cascode output impedance are much smaller than the drain-line skin-effect losses and can therefore be neglected. The TWA gain is then smaller than the cascode MAG.

For high bandwidths and high capacitive-division ratios (lower  $M$ ), the transistor area becomes larger, the per-section length of transmission lines decreases, and the number of cells increases. This causes two difficulties. First, there may be a physical layout problem because of the increased transistor sizes and reduced transmission line lengths. Second, as the number of cells increases, transmission-line skin-effect losses may limit the attainable gain from the amplifier. The skin-effect losses also need to be reduced. If a coplanar waveguide with a raised center conductor [5], [6] is used, both these difficulties are addressed.

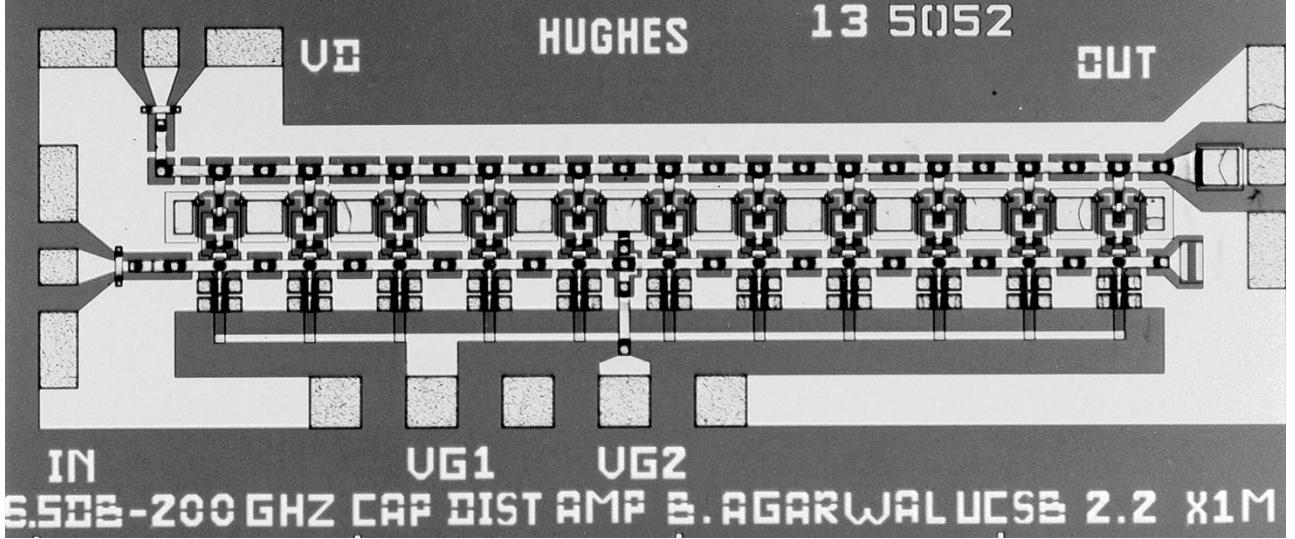

Fig. 9. Photomicrograph of the amplifier IC with 11 cells.

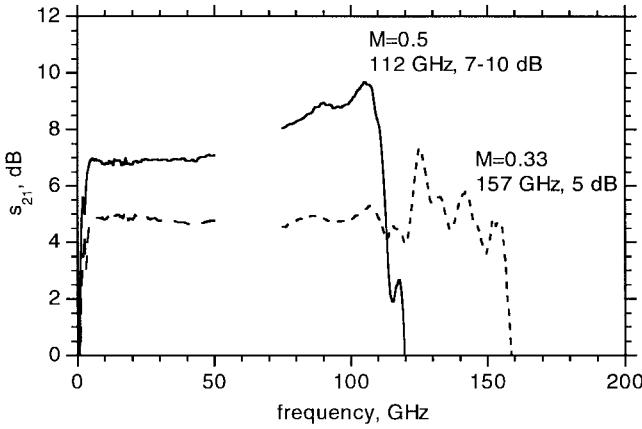

Fig. 10. Measured forward gain  $s_{21}$  of the two amplifiers.

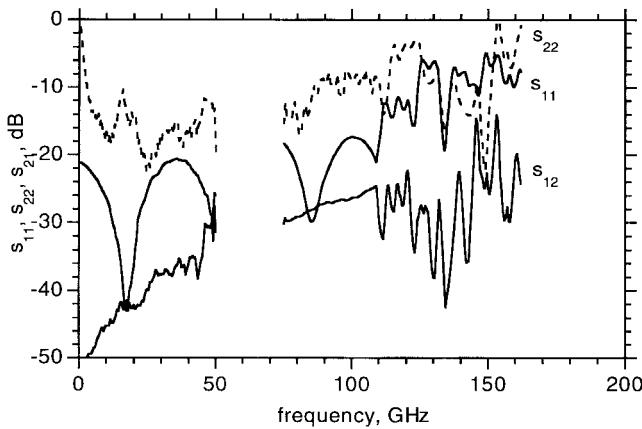

Fig. 11. Measured input return loss  $s_{11}$ , output return loss  $s_{22}$ , and reverse isolation  $s_{12}$  of the amplifier with 11 cells.

### III. CIRCUIT DESIGN AND FABRICATION

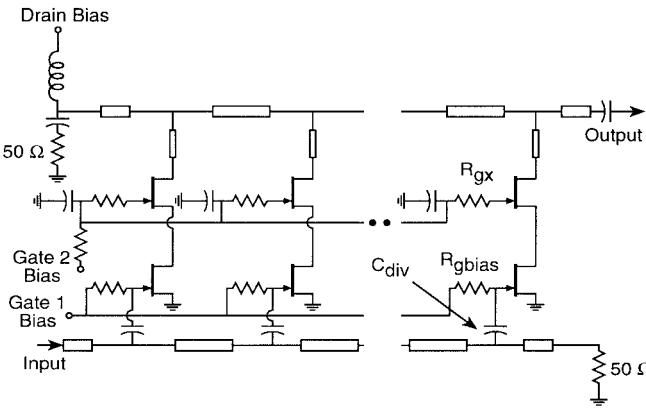

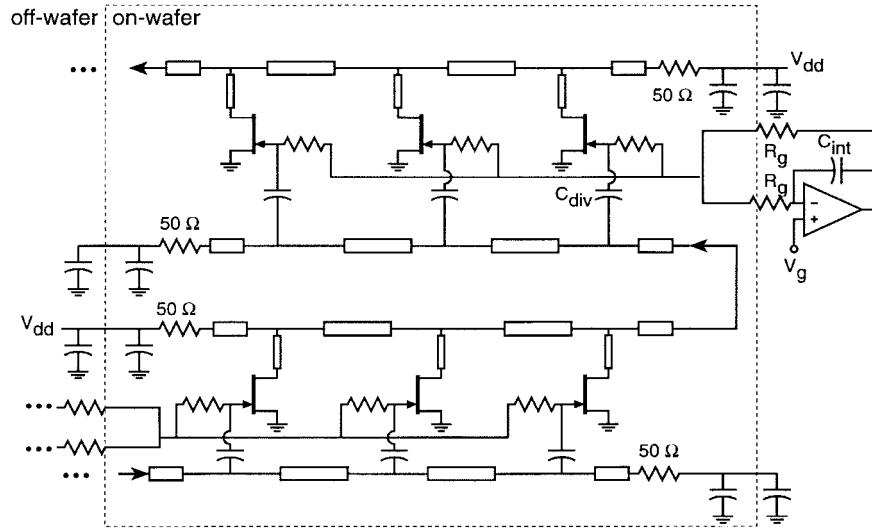

Using capacitive-division, cascode HEMT cells and coplanar waveguides with raised center conductors, two amplifiers were designed. Fig. 6 shows the circuit diagram. Cascode HEMT's  $Q1$  and  $Q2$  are used to reduce drain line losses

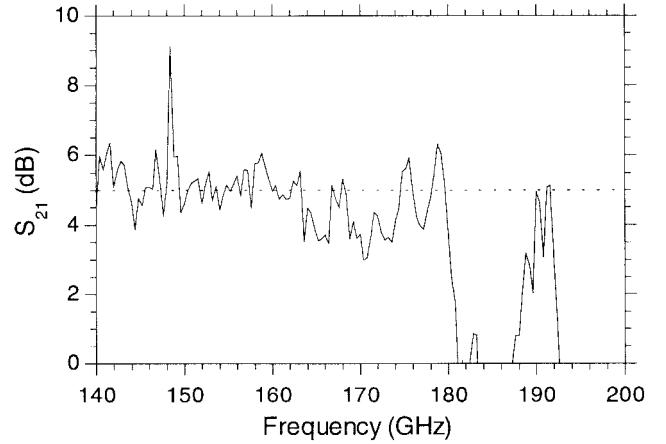

Fig. 12. Measured forward gain  $s_{21}$  for a TWA with 0.33:1 capacitive division and increased HEMT  $f_r$ .

and obtain high gain-bandwidth products. The gate and drain transmission lines are comprised of  $75\Omega$  coplanar waveguide sections with center conductors raised  $2\ \mu\text{m}$  off the substrate (Fig. 7). These lines have a measured velocity of  $1.78 \times 10^8\ \text{m/s}$  and a measured attenuation of  $0.22\ \text{dB/mm}$  at  $20\ \text{GHz}$ , increasing as the square root of frequency [6]. The drain line has a short  $90\Omega$  transmission line section for delay matching between the gate and drain lines.  $C_{\text{div}}$  is the division capacitor at the input of the common-source transistor.  $R_{gx}$ , a small damping resistor in the gate of the common-gate transistor, is inserted to provide unconditional amplifier stability.  $R_{g,\text{term}}$  is the  $50\Omega$  gate termination resistor.  $R_{d,\text{term}}$ , the drain termination resistor, and the drain bias are connected through an off-chip bias tee. This was done because an on-chip resistor did not have enough current capacity to withstand the drain bias current. The two gate bias connections are also shown.

Two amplifiers were designed. The first amplifier had 11 cascode cells with a capacitive division ratio of 0.33:1. The simulated gain and bandwidth were 7 dB and 210 GHz, respectively. The second amplifier had eight cells and a capacitive-division ratio of 0.5:1. For this amplifier, the simu-

Fig. 13. Interstage ac coupling networks for extended low-frequency response.

lated gain and bandwidth are 10 dB and 140 GHz, respectively. Fig. 8 shows the two simulations together with the cascode-cell MAG/MSG. The MAG/MSG of a single transistor is also shown for comparison. As the figure indicates, the gate damping resistor reduces the maximum cascode cell gain.

The designs were implemented in a 0.1- $\mu\text{m}$  gate length In-GaAs/InAlAs HEMT MMIC technology [9]. Typically, these HEMT's have  $f_{\max} = 300$  GHz and  $f_{\tau} = 160$  GHz. Fig. 9 shows a photomicrograph of the fabricated chip with 11 cells. The die size is about 2.2 mm  $\times$  1 mm.

#### IV. RESULTS

The amplifiers were tested on-wafer using commercial network analyzers from 0.045–50 GHz and 75–110 GHz. Beyond 110 GHz, we used in-house on-wafer network analysis based upon active probes [10]. Fig. 10 shows the measured forward gain  $s_{21}$  of the amplifiers. For the amplifier with 11 cells, the 3-dB bandwidth is 157 GHz and the gain is  $\approx 5$  dB. The eight-cell amplifier has 112 GHz bandwidth and 7–10 dB gain with a positive gain slope. The positive gain slope indicates that additional cells could have been added to this amplifier to obtain higher gain with a flatter response. The low frequency cutoff is about 1 GHz and is determined by the gate bias networks and by the output capacitor. Fig. 11 shows the input return loss  $s_{11}$ , the output return loss  $s_{22}$ , and the reverse isolation  $s_{12}$  of the amplifier. The amplifier output return loss  $s_{22}$  shows many resonances because of the off-chip drain-line termination.

The measured amplifier gains and bandwidths shown in Fig. 10 are lower than the design values because of low values of HEMT  $f_{\tau}$  ( $\approx 110$  GHz) on the tested wafer. Recently, a second process lot of amplifiers has been fabricated and tested. In this second process lot, using a modified HEMT design, the HEMT  $f_{\tau}$  and  $f_{\max}$  exceed the design values, and amplifier bandwidth is increased. These amplifiers were tested at NASA/JPL using a 140–220-GHz on-wafer vector network analysis system based upon harmonic mixers and waveguide-coupled micro-coaxial wafer probes. Measured over the 140–220 GHz band, the 11-stage amplifier exhibits 5 dB

gain and a 180-GHz high-frequency cutoff. As amplifier bias is varied, there is evidence of potential instability at 190 GHz.

We close with a comment on TWA applications. If TWA's are to be used in optical fiber links with standard nonreturn to zero (NRZ) line coding, the low frequency response must extend to a frequency  $\approx 10^5$  Hz smaller than the bit rate. Despite capacitive coupling, extended low-frequency response can be obtained in capacitive-division TWA's using the bias network of Fig. 13. Here, interstage dc blocking is provided by the (small) division capacitor  $C_{\text{div}}$ . A low-frequency cutoff of  $\approx 1$  MHz ( $f_{\text{low}} \approx 1/\pi R_g N C_{gs}$ ) can be obtained using a large dc bias resistor  $R_g \approx 1$  M $\Omega$ . With large values of  $R_g$ , dc bias errors will arise due to the HEMT gate leakage current. This can be suppressed by a closed-loop source/sense arrangement using an op amp integrator.

#### V. CONCLUSIONS

We have designed and fabricated TWA's having 1–112 GHz bandwidth with 7-dB gain and 1–157 GHz bandwidth with 5 dB gain. A third amplifier exhibited a 180-GHz high frequency cutoff with a 5-dB gain. Applications are in wideband instruments and in very high bit-rate fiber-optic systems.

#### ACKNOWLEDGMENT

The authors would like to acknowledge the support of P. Greiling of Hughes Research Laboratories and M. Delaney of Hughes Space and Communications Company for this work. They would like to thank R. Pullela of UCSB and L. Samoska and T. Gaier of JPL for helping with on-wafer millimeter-wave network measurements.

#### REFERENCES

- [1] R. Majidi-Ahy, C. K. Nishimoto, M. Riazat, M. Glenn, S. Silverman, S.-L. Weng, Y.-C. Pao, G. A. Zdziuk, S. G. Bandy, and Z. C. H. Tan, "5–100 GHz InP coplanar waveguide MMIC distributed amplifier," *IEEE Trans. Microwave Theory Tech.*, vol. 38, pp. 1986–1993, 1990.

- [2] J. Pusl, B. Agarwal, R. Pullela, L. D. Nguyen, M. V. Le, M. J. W. Rodwell, L. Larson, J. F. Jensen, R. Y. Yu, and M. G. Case, "Capac-

- itive division traveling wave amplifier with 340 GHz gain-bandwidth product," in *IEEE Microwave and Millimeter-Wave Monolithic Circuits Symp. Tech. Dig.*, 1995, pp. 175–178.

- [3] S. Kimura, Y. Imai, and T. Enoki, "0–90 GHz InAlAs/InGaAs/InP HEMT distributed baseband amplifier IC," *Electron. Lett.*, vol. 31, pp. 1430–1431, 1995.

- [4] Y. Ayasli, S. W. Miller, R. Mozz, and L. K. Hanes, "Capacitively coupled traveling-wave power amplifier," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-30, pp. 976–981, 1982.

- [5] M. S. Shakouri, A. Black, B. A. Auld, and D. M. Bloom, "500 GHz GaAs MMIC sampling wafer probe," *Electron. Lett.*, vol. 29, pp. 557–559, 1993.

- [6] U. Bhattacharya, S. T. Allen, and M. J. W. Rodwell, "DC-725 GHz sampling circuits and subpicosecond nonlinear transmission lines using elevated coplanar waveguide," *IEEE Microwave Guided Wave Lett.*, vol. 5, pp. 50–52, 1995.

- [7] Y. Ayasli, R. L. Mozz, J. L. Vorhaus, L. D. Reynolds, and R. A. Pucel, "A monolithic GaAs 1–13 GHz traveling-wave amplifier," *IEEE Trans. Electron Devices*, vol. 31, pp. 1937–1942, 1984.

- [8] M. J. W. Rodwell, S. T. Allen, R. Y. Yu, M. G. Case, U. Bhattacharya, M. Reddy, E. Carman, M. Kamegawa, Y. Konishi, J. Pusl, and R. Pellela, "Active and nonlinear wave propagation devices in ultrafast electronics and optoelectronics," *Proc. IEEE*, vol. 82, pp. 1037–1059, 1994.

- [9] L. Nguyen, M. Le, M. Delaney, M. Lui, T. Liu, J. Brown, R. Rhodes, M. Thompson, and C. Hooper, "Manufacturability of 0.1  $\mu$ m millimeterwave low-noise InP HEMT's," in *IEEE MTT-S Int. Microwave Symp. Tech. Dig.*, 1993, pp. 345–347.

- [10] R. Y. Yu, M. Reddy, J. Pusl, S. T. Allen, M. Case, and M. J. W. Rodwell, "Millimeter-wave on-wafer waveform and network measurements using active probes," *IEEE Trans. Microwave Theory Tech.*, vol. 43, pp. 721–729, 1995.

- [11] R. Lai, H. Wang, Y. C. Chen, T. Block, P. H. Liu, D. C. Streit, D. Tran, P. Siegel, M. Barsky, W. Jones, and T. Gaier, "D-band MMIC LNA's with 12 dB gain at 155 GHz fabricated on a high yield InP HEMT MMIC production process," in *Int. Conf. Indium Phosphide Related Materials Tech. Dig.*, 1997, pp. 241–244.

**Bipul Agarwal**, for photograph and biography, see this issue, p. 2306.

**Adele E. Schmitz** received the B.S. degree in chemistry with honors from Pepperdine University, Malibu, CA, in 1979. She later received the M.S.E.E. degree from the University of California, Los Angeles, in 1993. Her masters thesis was on the design, modeling, and fabrication of InP-based inverted HEMT's. She joined Hughes Research Laboratories, Santa Barbara, CA, in 1977 and initially worked on the testing and evaluation of nickel-cadmium batteries for satellite applications, plasma polymerized films as protective coatings for IR optics, and the fabrication of GaAs integrated circuits using all e-beam lithography. From 1982 to 1989, she designed, modeled, and fabricated sub-half-micrometer devices for bulk silicon and silicon-on-sapphire VLSI technologies. Her work included the circuit fabrication of a 1.9-GHz 4-bit analog-to-digital converter built in 0.25-mm CMOS/SOS technology. Since 1989, she has been developing reliable InP-based high electron mobility transistors for power, low-noise, and optoelectronic applications. She is currently a Senior Project Engineer in charge of the fabrication of InP-based HEMT MMIC's and discrete devices.

**J. J. Brown**, photograph and biography not available at the time of publication.

**Mehran Matloubian** received the Ph.D. degree in electrical engineering from the University of California at Los Angeles (UCLA) in 1989. His academic research work was on microwave and millimeter-wave characterization of transistors and dielectric materials.

He joined the Hughes Research Laboratories, Santa Barbara, CA, in 1990 working on the development of InP-based power HEMT's and MMIC's. He is currently Manager of the MMIC Design Department and Program Manager for the advanced HEMT technology development at HRL Laboratories. He has authored or co-authored more than 90 publications and presentations and has 11 patents.

**Michael G. Case** (S'87–M'93–SM'98) was born in 1966 in Ventura, CA. After receiving the B.S. degree in 1989 from the University of California, Santa Barbara, he began research there under a State Fellowship for Prof. M. Rodwell. In Dr. Rodwell's group, he studied nonlinear transmission lines for applications in high-speed waveform shaping and signal detection. He earned the M.S. and Ph.D. degrees in 1991 and 1993, respectively, from U.C. Santa Barbara. The Air Force Office of Scientific Research sponsored a majority of his work.

Since 1993 he has been employed by HRL Laboratories (previously the Hughes Aircraft Company's research labs), Malibu, CA. He is currently involved with millimeter-wave device characterization, circuit design, and measurement techniques.

**M. Le**, photograph and biography not available at the time of publication.

**M. Lui**, photograph and biography not available at the time of publication.

**Mark J. W. Rodwell**, for photograph and biography, see this issue, p. 2307.